Credit: MIT

The cutting edge of AI and chip making is the integration of intelligence into a variety of applications so they work better by increasing productivity, efficiency and connectivity. This concept is often referred to as embedded intelligence. While there have been some major leaps in recent years in the fields of artificial intelligence and machine learning, computer chips are lagging in throughput to fully power embedded intelligence. In computers and many other devices today there is a chip for computing and a separate chip for data storage. The interaction between the two are limited. As applications are required to handle massively growing volumes of data, the limited rate at which data can be pushed through between two or more chips meant to be working in harmony together is creating a critical communication slowdown. And with limited space, there is not enough room to place the chips side-by-side (a phenomenon known as Moore’s Law), even as they have been miniaturized. Adding to this technical roadblock underlying devices like transistors, are no longer improving at the meteoric rate that they have for decades.

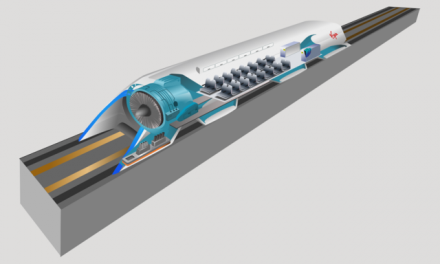

The new 3-D computer chip architecture

In a paper published in the journal Nature researchers at Stanford University and MIT have built a new chip that uses multiple nanotechnologies, together with a new computer architecture, to address many of these throughput issues. Such an architecture is not possible with existing silicon-based technology, so the chip instead uses carbon nanotubes. The carbon nanotubes, are sheets of 2-D graphene formed into nanocylinders. The nanocylinders feature resistant random-access memory (RRAM) cells, a type of nonvolatile memory that operates by changing the resistance of a solid dielectric material. The researchers believe this is the most complex nanoelectronic system ever made. The researchers leveraged several emerging nanotechnologies to integrate over 1 million RRAM cells and 2 million carbon nanotube field-effect transistors. To improve communication the team built dense 3-D computer architecture with interleaving layers of logic and memory. The architectural design features the RRAM and carbon nanotubes built vertically over one another. Then they inserted ultradense wires between these layers.

A demonstration of the new chips abilities

To test and demonstrate the viability of this new 3-D chip technology the team of researchers built a new embedded application using the ability of carbon nanotubes to also act as sensors to detect and classify ambient gases. To do this they placed over 1 million carbon nanotube-based sensors on the top layer of the chip. The layering of sensing, data storage, and computing together, allowed the chip to measure each of the sensors in parallel, and then write directly into its memory, with the successful outcome of generating huge bandwidth.

Next Steps

While the team will continue working to improve the underlying nanotechnologies, the paper’s lead author, Max Shulaker, who is a core member of MIT’s Microsystems Technology Laboratories, is collaborating with Massachusetts-based semiconductor company Analog Devices to develop new versions of the chip architecture that further exploits the tandem ability of sensing and data processing on the same chip.